Victor Peng, generální ředitel Xilinx na Xilinx Developer Forum (XDF) odhalil produkty, které jak doufá, zvýší podíl společnosti na trhu v oblasti cloud, enterprise data center a umělé inteligence.

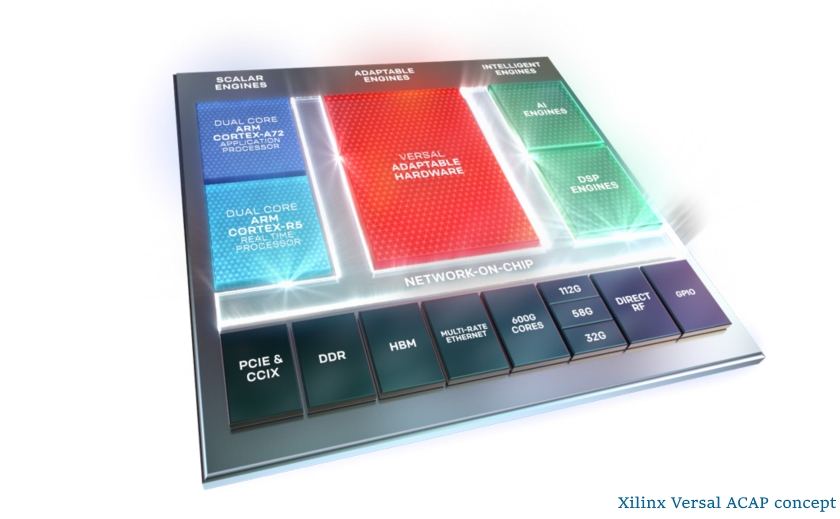

Peng oznámil zařízení nazvané „Versal“, které se hodí do nové kategorie produktů – adaptivní výpočetní akcelerační platformy (ACAP). Hlavní myšlenka architektury ACAP – s rozpočtem na výzkum a vývoj ve výši 1 miliardy dolarů – spočívá v přijetí heterogenní výpočetní techniky s rozdílnými koprocesory, které se používají při řešení různých úkolů.

Versal přichází v šesti variantách; všechny budou mít field programmable gate array (FPGA), spojené s dvěma armádami Cortex-A72 a Cortex-R5.

Zařízení budou obsahovat 256 kB paměti na čipu s ECC, více než 1 900 DSP a více než 1,9 milionu systémových logických buněk v kombinaci s více než 130Mb UltraRAM, až 34Mb blokové paměti RAM, 28Mb distribuované paměti RAM a 32Mb nových Accelerator RAM bloků.

Serie Versal zahrnuje také 8-lane a 16-lane PCIe Gen4 a hostitelské rozhraní CCIX, 32G SerDes, až čtyři integrované řadiče paměti DDR4, až čtyři multi-rychlostní ethernetové MAC.

To vše je propojeno network-on-chip (NoC) s až 28 porty master / slave. Křemík bude vyrábět společnost TSMC za použití 7-nm procesu FinFET.

Představujeme Alveo

Na XDF Xilinx představil také Alveo, portfolio akcelerátorových karet pro servery datových center.

Alveo U200 a Alveo U250 jsou vybaveny technologií Xilinx UltraScale + FPGA, přičemž firma tvrdí, že se výrazně zlepšuje strojové učení při lepší propustnosti procesorů. Peng a AMD CTO Mark Papermaster se na scéně XDF rozhodli ustavit nový světový rekord pro propustnost – 30 000 snímků za sekundu – pomocí osmi karet Alveo U250 a dvou serverů AMD Epyc 7551. Benchmark byl proveden v GoogleNet.